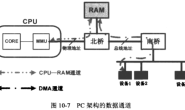

1 Main memory RAM configuration:

Zeroed at power-up for cold-boot to prevent parity errors.

Configured and enabled by ROM code at system power-up.

2 Cache memory RAM configuration:

Usually disabled at power-up, enabled by VxWorks pre-kernel initialization code.

Provide cache management libraries.

For some architectures the instruction cache is enabled at power-up for faster VxWorks boots.

3 ROM – Non-volatile property allows:

System boot code storage.

Hardware environment configured to jump to a ROM address atpower-up.

To program a ROM, it is removed from hardware environment and taken to a ROM “burner”.

4 Flash

(1) Flash is non-volatile memory which can be modified programmatically.

(2) Used as a “silicon” hard disk:

<1> System boot code storage.

<2> Hardware environment configured to jump to a flash address atpower-up.

<3> Maintaining data integrity during power-outs.

<4> Access times slightly slower than DRAM but faster than

ROM.

5 Flash vs PROM

(1) Flash and ROM use similar memory cell technology:

<1> Storage transistor employs transistor tunnelling.

<2> No battery to provide non-volatility.

<3> Access times are roughly the same.

(2) Flash power supply unit allows flashto be modified without being removed from hardware environment.

<1> Contents may be modified over a network interface.

<2> Contents may be modified by application code.

<3> ICE maybe a savior when bootloader within flash crash.

(3) Many hardware environments use jumpers to configure:

<1> System to jump to a flash address or a PROM address atpower-up.

<2> Size of on board flash/PROM.

6 NVRAM

(1) Non-volatile RAM:

<1> Non-volatility usually provided by battery.

<2> May be implemented using CMOS RAM, battery-backed SRAM, or flash.

(2) Units may contain a programmable time-of-day (TOD) clock:

<1> TOD information is stored inNVRAM.

(3) Used to store boot parameters for VxWorks image:

<1> VxWorks boot parameters may useup 255 bytes.

(4) If a hardware environment does not have NVRAM, boot parameters are statically linked into boot code.

Declaration:

Excerpt from Chapter 2 System Hardware, 2.4 Memory Of 《Tornado BSP training workshop》